一、实验目的:设计实现呼吸灯,并对代码进行仿真。

二、ZYNQ工程建立

1.新建工程,前文有详细的建立工程过程,这里不再赘述。

三、呼吸灯的实现

1.添加代码

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: yu meng ya

//

// Create Date: 2022/04/30 14:42:23

// Design Name: 呼吸灯

// Module Name: breath_led_tb

// Project Name: fpga_breath_led

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module breath_led #

(

parameter CLOCK_FRQ=50000000,//输入时钟频率50M

parameter PWM_FRQ=1000,//PWM频率1K

parameter BREATH_ERIOD=2,//呼吸周期 2S

parameter SET_COMPARE_FRQ=1000,//比较输出频率 1K

parameter PWM_COUNTER_MAX=CLOCK_FRQ/PWM_FRQ,//PWM发生计数最大值

parameter BREATH_COUNTER_MAX=CLOCK_FRQ*BREATH_ERIOD,//呼吸计数最大值

parameter SET_COMPARE_COUNTER_MAX=CLOCK_FRQ/SET_COMPARE_FRQ,//设置的比较计数最大值

parameter COMPARE_VALUE_STEP=PWM_COUNTER_MAX/SET_COMPARE_FRQ//比较值的步长

)

(

input wire clk,

input wire rstn,

output wire [3:0]led

);

reg [31:0]counter_pwm;

reg [31:0]counter_breath;

reg [31:0]counter_compare;

reg [31:0]compare_value;

reg pwm_period_clk_view;

reg breath_period_clk_view;

reg compare_period_clk_view;

reg [3:0]led_number;

reg led_breath_view;

reg breath_dir;

reg [3:0]led_reg;

assignled=led_reg;

//led的值输出

always @(posedge clk)

begin

if(rstn==0)led_reg<=0;

case (led_number)

8'b000:led_reg[0]<=led_breath_view;

8'b001:led_reg[1]<=led_breath_view;

8'b010:led_reg[2]<=led_breath_view;

8'b011:led_reg[3]<=led_breath_view;

default: led_reg[0]<=led_breath_view;

endcase

end

//pwm

always @(posedge clk or negedge rstn)

begin

if(rstn==0)

begin

counter_pwm<=0;

pwm_period_clk_view<=0;

end

else

begin

counter_pwm<=counter_pwm+1;

if(counter_pwm<compare_value)led_breath_view<=1;

else led_breath_view<=0;

if(counter_pwm>PWM_COUNTER_MAX-1)

begin

counter_pwm<=0;

pwm_period_clk_view<=~pwm_period_clk_view;

end

end

end

//led输出逻辑

reg [3:0]led_number_state;

always @(posedge clk or negedge rstn)

begin

if(rstn==0)

begin

led_number=0;

counter_breath<=0;

breath_period_clk_view<=0;

breath_dir<=0;

led_number_state<=0;

end

else

begin

counter_breath<=counter_breath+1;

if(counter_breath>BREATH_COUNTER_MAX-1)

begin

counter_breath<=0;

breath_period_clk_view<=~breath_period_clk_view;

breath_dir<=~breath_dir;

if(breath_dir==1)

begin

case (led_number_state)

0:begin led_number_state=1;led_number=0;end

1:begin led_number_state=2;led_number=1;end

2:begin led_number_state=3;led_number=2;end

3:begin led_number_state=4;led_number=3;end

4:begin led_number_state=5;led_number=2;end

5:begin led_number_state=6;led_number=1;end

6:begin led_number_state=0;led_number=0;end

default:begin led_number_state=0;led_number=0;end

endcase

end

end

end

end

//呼吸逻辑和向上向下计数逻辑

always @(posedge clk or negedge rstn)

begin

if(rstn==0)

begin

counter_compare<=0;

compare_period_clk_view<=0;

compare_value<=0;

end

else

begin

counter_compare<=counter_compare+1;

if(counter_compare>SET_COMPARE_COUNTER_MAX-1)

begin

counter_compare<=0;

if(breath_dir==0)

begin

if(compare_value<PWM_COUNTER_MAX)compare_value<=compare_value+COMPARE_VALUE_STEP;

end

else if(breath_dir==1)

begin

if(compare_value>0)compare_value<=compare_value-COMPARE_VALUE_STEP;

end

compare_period_clk_view<=~compare_period_clk_view;

end

end

end

endmodule

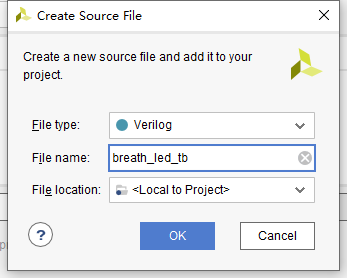

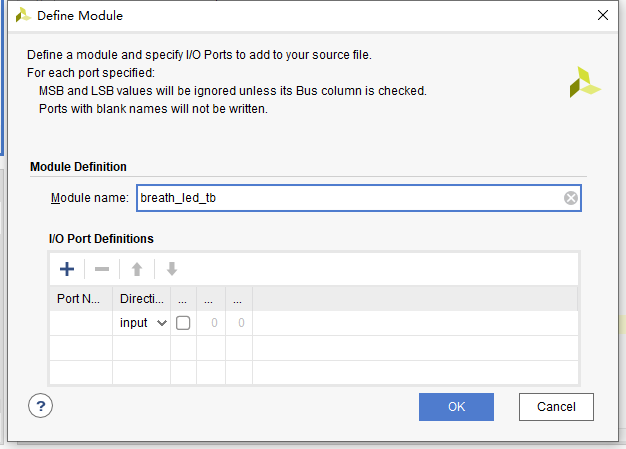

四、新建Verilog的testbench文件

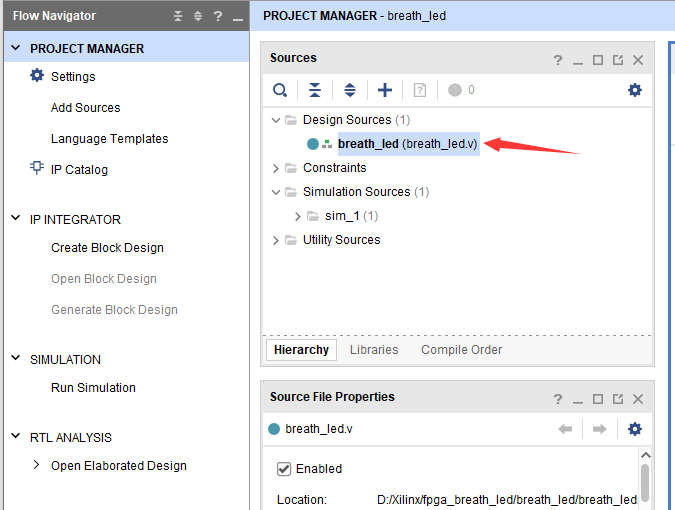

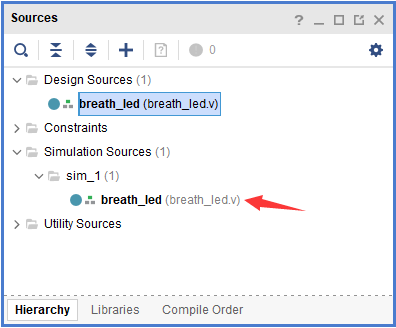

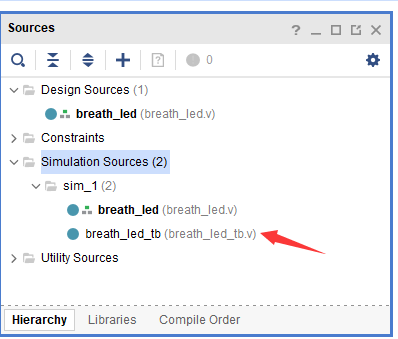

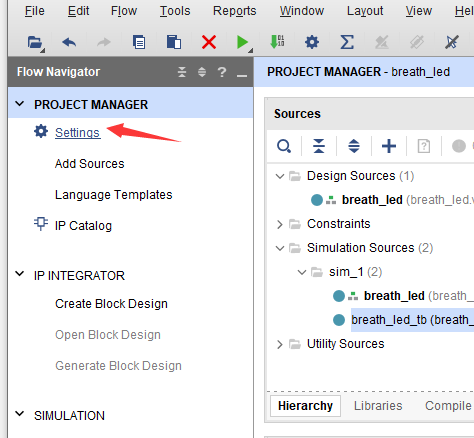

1. 可以看见simulation sources-->sim_1也出现了breath_led文件。

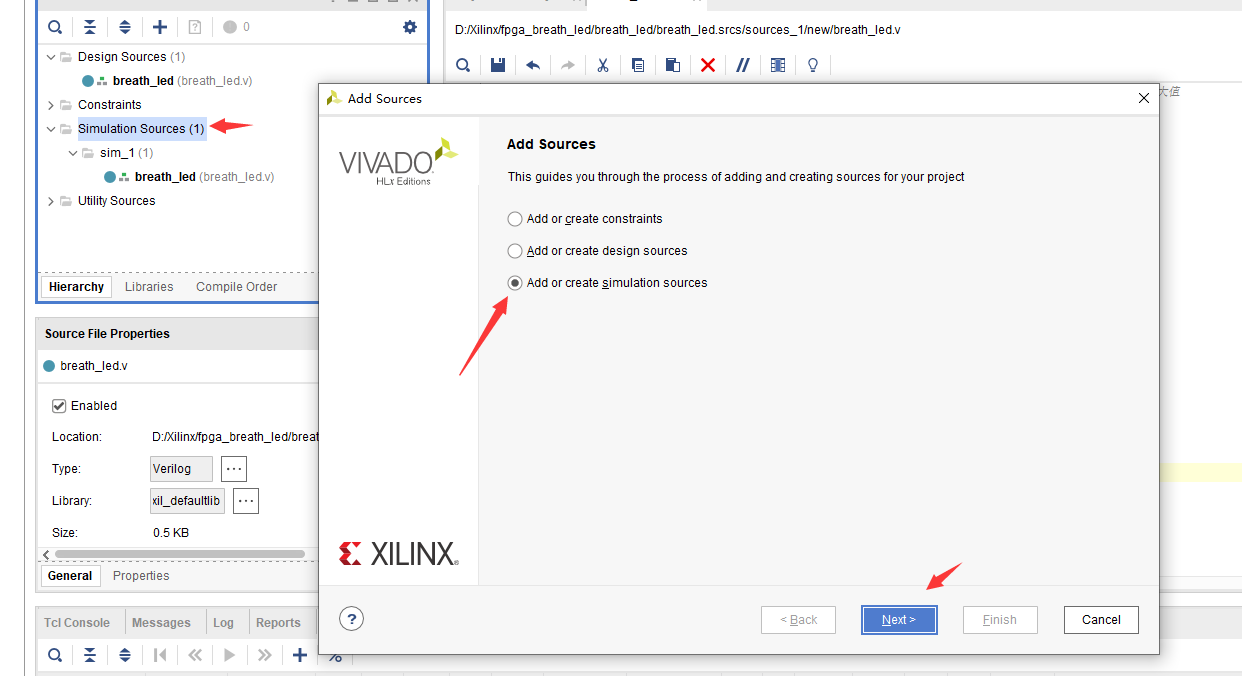

2. simulation sources右键,点击next。

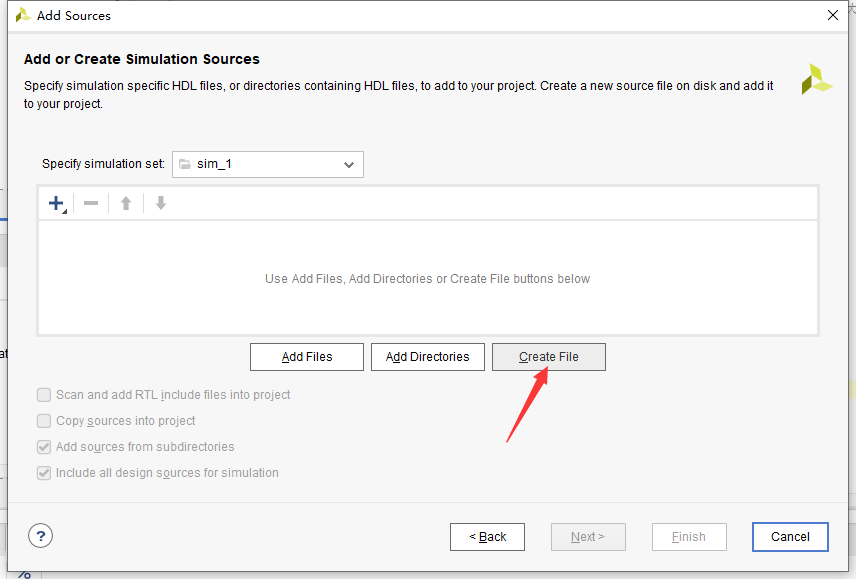

3. 点击create file

4. 命名仿真文件,点击OK

5. 点击finish,完成testbench文件添加,点击OK

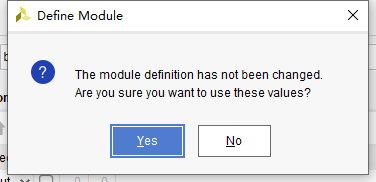

6.点击yes

7.可以看见一个breath_led_tb文件

8. 然后编辑仿真文件

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: yu meng ya

//

// Create Date: 2022/04/30 14:42:23

// Design Name: 呼吸灯测试

// Module Name: breath_led_tb

// Project Name: fpga_breath_led

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module breath_led_tb();

reg clk_reg ;

reg rstn_reg ;

wire [3:0] led ;

wire clk ;

wire rstn ;

initial begin

clk_reg = 0;

rstn_reg = 0 ;

#10

rstn_reg = 1 ;

end

always#1 clk_reg =~clk_reg ;

assign rstn = rstn_reg ;

assign clk = clk_reg ;

breath_led

#(

.CLOCK_FRQ(1000000)

)

breath_led_inst

(

.clk (clk),

.rstn (rstn) ,

.led (led)

);

endmodule

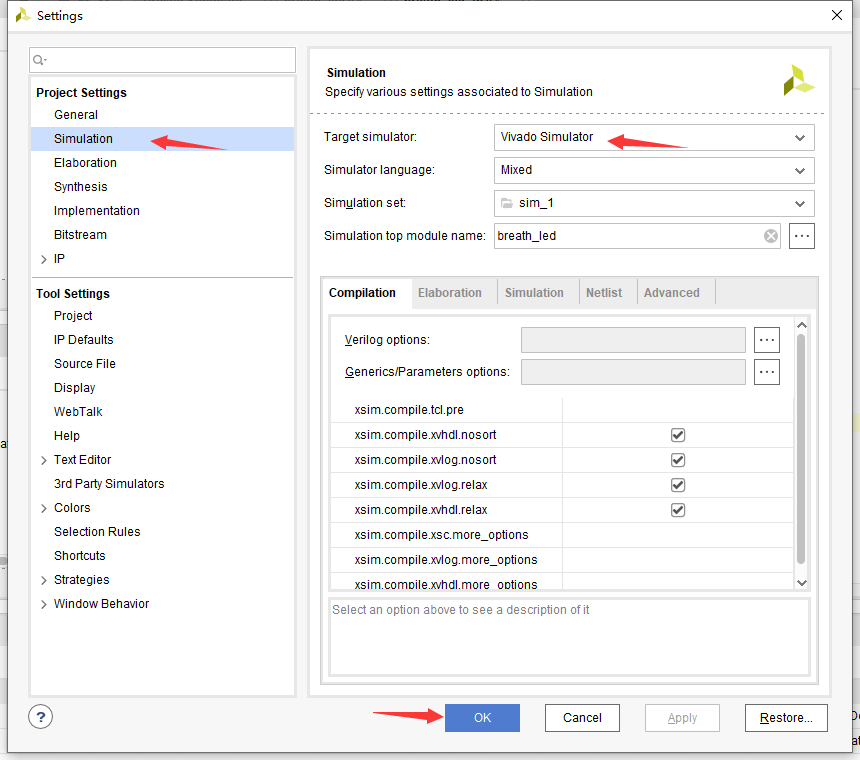

9. 为了提高仿真验证速度,将时钟信号参数改为100000HZ,通过参数传递的形式修改。点击settings

10. 点击simulation,选择Vivado simulation,点击OK

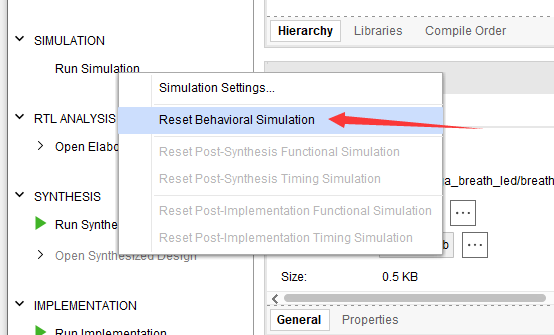

11.右键run simulation,选择reset

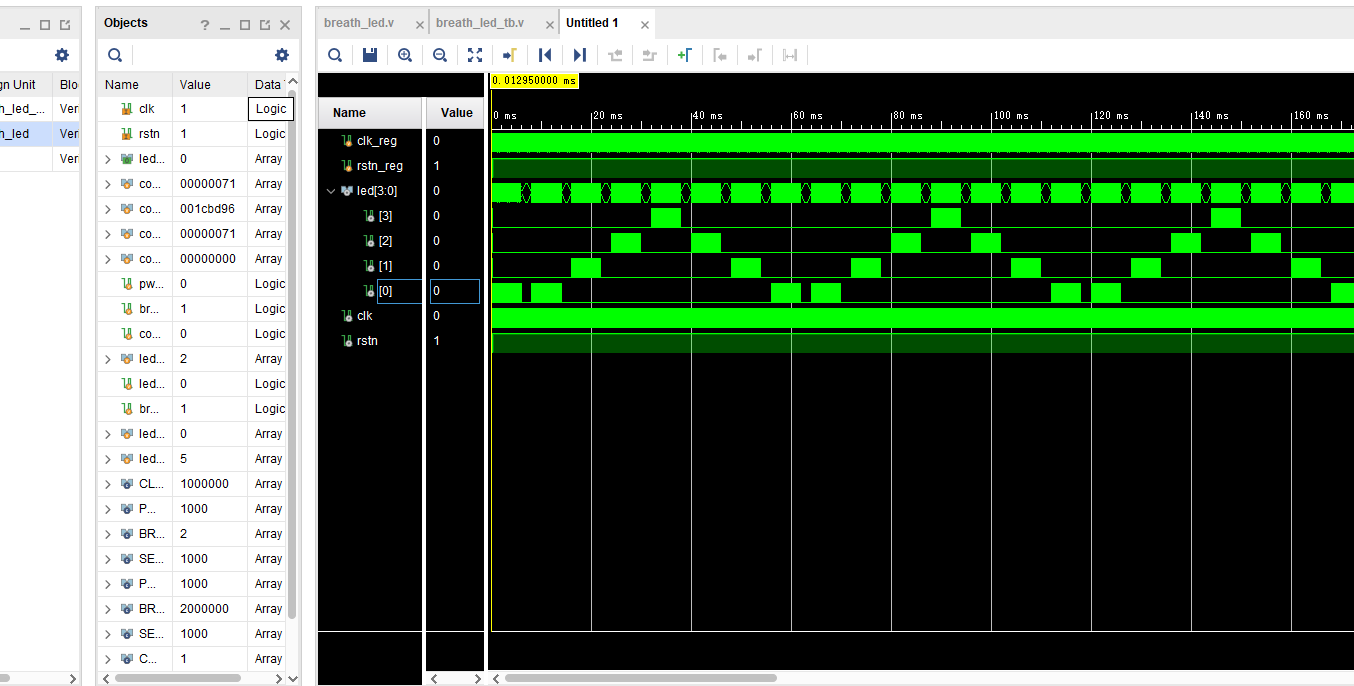

12. 出现仿真波形

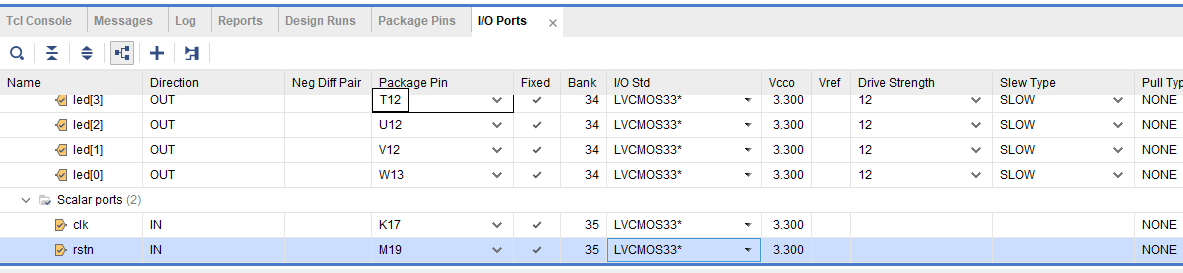

13.引脚绑定,点击open Elaborated Design

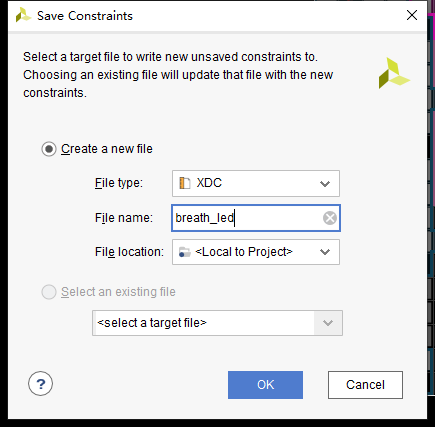

14.保存,命名然后点击ok

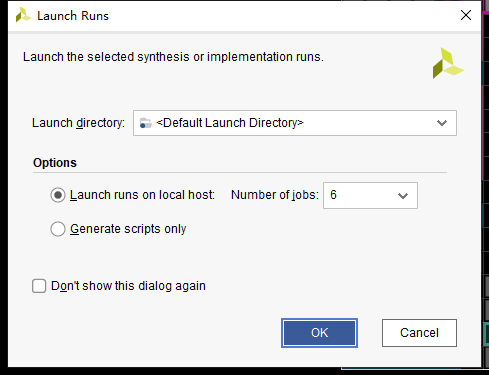

15.PROGRAM AND DEBUG 下面的 Generate Bitestream 生成 BIT 文件。选择yes。

16.选择OK

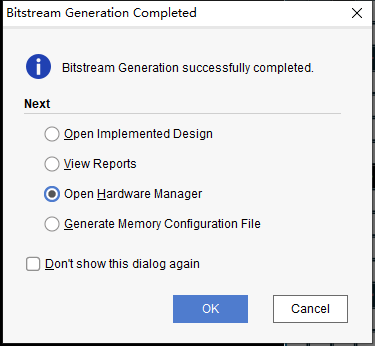

17.等待软件运行这些操作结束,点击 Open Hardware Mnager ,点击ok。

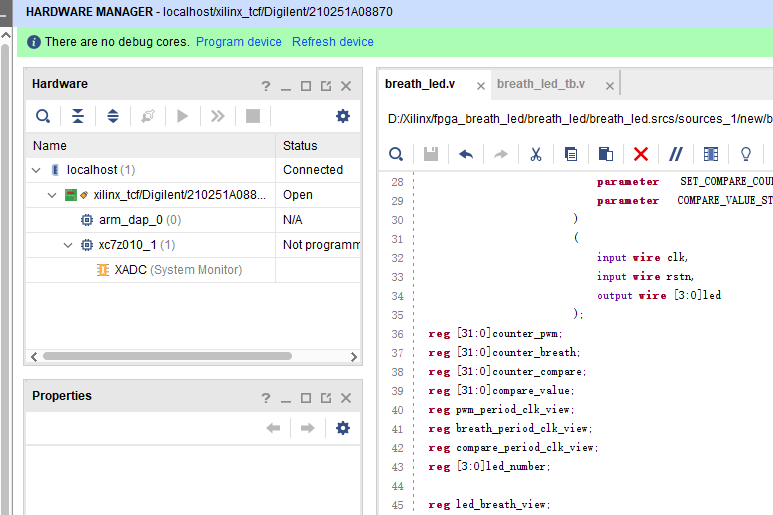

18.弹出的硬件管理界面,这个时候可以插上我们的ZYNQ MINI开发板的下载器USB接口,然后点击 Open target,选择Auto Connect。

可以看到 Hardware 窗口出现了两个设备,一个是 arm 的 dap,一个是 xc7z010 芯片。上方我们点击 Program Device 进行烧写配置。

19.保持默认,点击program,可以看见板子上出现了呼吸灯的效果。