I2C通信协议

i2c(inter-integrated Circuit 集成电路总线)总线支持设备之间的短距离通信,用于处理器和一些外围设备之间的接口,需要两根信号线来完成信息交换。

I2C协议把传输的消息分为两种类型的帧。地址帧:用于master指明消息发往哪个slave;数据帧:用于master发送数据到slave或者接收slave的数据;一次读写单位为8bit。

I2C的数据传输

在数据传输时,时钟信号为高电平期间,数据线上的数据保持稳定。只有在时钟信号为低电平期间,数据线上的高电平或者低电平才允许变化。数据在时钟SCL上升沿到来之前就需要准备好,在SCL下降沿之前保持稳定。

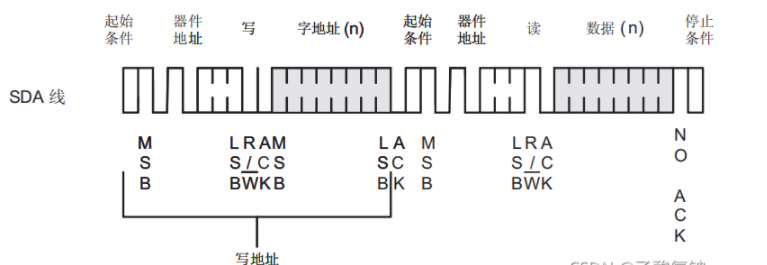

主设备往从设备中写寄存器,数据的传输格式:

①首先由主机发送一个开始信号

②主机在数据线上广播从机地址

③确定数据的传输方向是写

④“A”代表应答,代表主机找到了从机

⑤主机发送一个字节数据,从机接收到后,会返回主机一个应答信号。当主机发送完数据,或者从机返回了一个NACK信号,表示从机不再接收主机的数据。主机发送一个STOP信号,表示数据传输完成。

主设备读取从机的寄存器值:

①主机发送一个开始信号

②主机在数据线上广播从机的地址

③确定数据的传输方向读

④从机返回应答信号,表示主机找到了从机

⑤从机返回读的数据

⑥主机返回一个应答信号,表示成功接收到从机发出的一个数据

⑦当主机接收完数据,返回一个非应答信号NACK,从机释放数据总线,接着主机发送一个STOP信号,表示此次数据传输结束。

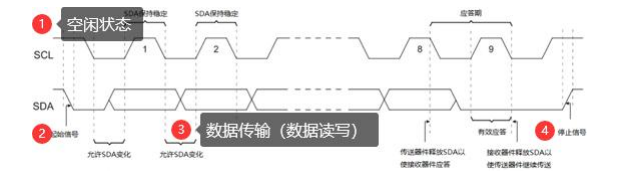

I2C时序

① IIC 协议空闲状态

② IIC 协议的起始信号

③ IIC 协议的数据传输(数据读写)状态(应答信号(ACK))

④ IIC 协议的停止信号

I2C空闲状态

图中标注①表示“总线空闲状态”,在此状态下串口时钟信号 SCL 和串行数据信号 SDA 均保持高电平(都为 1),此时无 IIC 设备工作。

I2C起始信号

图中标注②表示“起始信号”,在 IIC 总线处于“空闲状态”时, 时钟信号线 SCL 为高电平时,数据信号线 SDA 被拉低(由高电平变为 低电平),出现下降沿,表示产生了一个起始信号。起始信号是由主机(本实验中为 FPGA)主动建立的,在建立该信号之前 IIC 总线必须处于空闲状态。

I2C数据传输(数据读写)状态

IIC 通讯设备的通讯模式是主从通讯模式,通讯双方有主从之分。 数据信号线 SDA 更新数据时:在时钟信号线 SCL 为低电平时将数据信号线 SDA 上的数据进行数据更新。 即数据在时钟信号线 SCL 的上升沿到来之前就必须准备好,并在 SCL 下降沿到来之前必须保持稳定。

应答信号(ACK)

IIC 总线上的所有数据都是以字节(8bit)传送的,发送端(可以 是主机也可以是从机)每发送一个字节(8bit),就必须在第 9 个 SCL 脉冲期间释放 SDA,由接收端(发送端为主机时,接收端为从机/发 送端为从机时,接收端为主机)反馈一个应答信号。

应答信号为低电平(为 0)时,称为有效应答位(ACK),表示接 收端成功接收了该字节(8bit);应答信号为高电平(为 1)时,称 为非应答位(NACK),表示接收端接收该字节(8bit)失败。

注:数据接收失败或者数据传输结束都要发送 NACK。

反馈有效应答位(ACK):接收端在第 9 个时钟脉冲之前的低电平期 间将 SDA 拉低,并且确保在该时钟周期的高电平期间保持低电平。

I2C停止信号

数据读写完成后,时钟信号线 SCL 为高电平时,数据信号线 SDA 被释放(由低电平转为高电平),出现上升沿,表示产生了一个停止 信号,IIC 总线跳转回“总线空闲状态”。 停止信号是由主机(本实验中为 FPGA)主动建立的,建立该信号 之后,IIC总线将返回空闲状态。

优点

仅使用两根电线

支持多个主机和多个从机

硬件比UART更简单

众所周知且被广泛使用的协议

缺点

数据传输速率比SPI慢

数据帧的大小限制为8位

I2C读写EEPROM

EEPROM 的写操作有:

①单字节写(BYTE WRITE)

② 页写(PAGE WRITE)

EEPROM 的读操作有:

①当前地址读(Current Address READ)

②随机地址读(RANDOM READ)

③顺序地址读(SEQUENTIAL READ

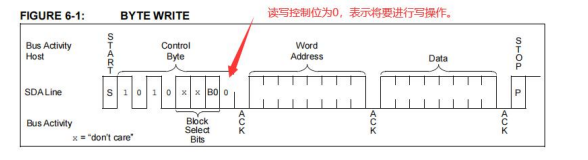

EEPROM单字节写操作时序

字节写(BYTE WRITE)操作:在数据信号线 SDA 上,发起始位 (START)->写写控制字(Control Byte)->接收 ACK->写字节地址(Word Address)->接收 ACK->写数据(Data) ->接收 ACK->发停止位(STOP)。

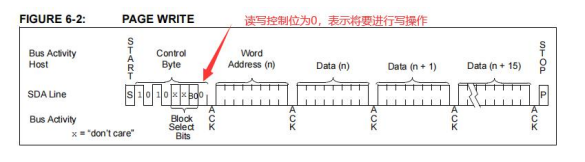

EEPROM页字节写操作时序

页写(PAGE WRITE)操作:一次写入 16 个字节(每字节为 8bit)数据。 在数据信号线 SDA 上,发起始位(START)->写写控制字(Control Byte)-> 接收 ACK->写字节地址(Word Address)->接收 ACK->写数据(Data(n)) -> 接收 ACK->写数据(Data(n+1))->接收 ACK->(一共发送 16 字节(Byte) 数据,中间数据省略)->写数据(Data(n+15))->接收 ACK->发停止位 (STOP)。

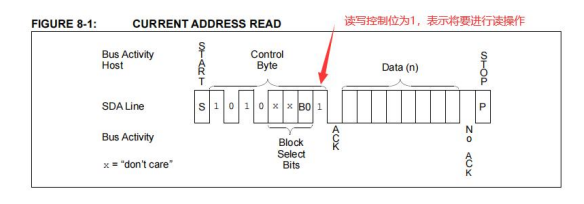

EEPROM当前地址读操作时序

当前地址读(Current Address READ)操作:在数据信号线 SDA 上, 发起始位(START)->写读控制字(Control Byte)->接收 ACK->接收读数据 (Data)->发 No ACK ->发送停止位(STOP)。

EEPROM随机读操作

随机读需先写一个目标字地址,一旦EEPROM接收器件地址和字地址并应答了ACK,主器件就产生一个重复的起始条件。然后,主器件发送器件地址(读/写选择位为"1"),EEPROM应答ACK,并随时钟送出数据。主器件无需应答"0",但需发送停止条件。

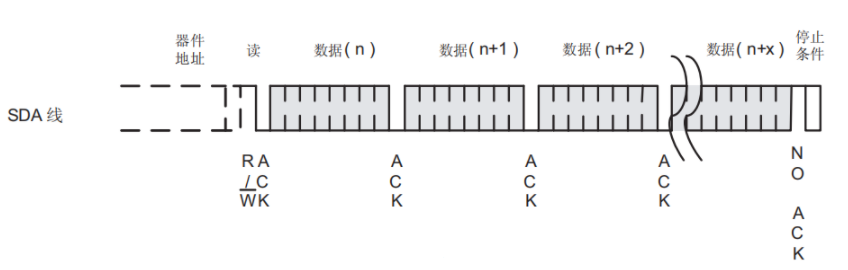

EEPROM顺序读操作

顺序读可以通过“当前地址读”或"随机读”启动。主器件接收到一个数据后,应答ACK,只要EEPROM接收到ACK,将自动增加字地址并继续随时钟发送后面的数据。若达到存储器地址末尾,地址自动回转到0,仍可继续顺序读取数据。主器件不应答"0",而发送停止条件,即可结束顺序读操作。

SPI通信协议

SPI(Serial Peripheral Interface)串行外设接口,是一种高速的,全双工,同步的通信总线。它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设备FLASH、RAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI通信原理

SPI以主从方式工作,通常有一个主设备和一个或者多个从设备,需要至少4根线。

1、这是一个主机的通讯时序。NSS、SCK、MOSI信号都由主机控制产生,而MISO的信号由从机产生,主机通过该信号线读取从机的数据。MOSI与MISO的信号只在NSS为低电平的时候才有效,在SCK的每个时钟周期MOSI和MISO传输一位数据。

2、SPI使用MOSI及MISO信号线来传输数据,使用SCK信号线进行数据同步。MOSI及MISO数据线在SCK的每个时钟周期传输一位数据,且数据输入输出是同时进行的。数据传输时,MSB(高位)先行或LSB(低位)先行并没有作硬性规定,但要保证两个SPI通讯设备之间使用同样的协定。

①MISO--Master Input Slave Output ,主设备数据输入,从设备数据输出。

②MOSI--Master Output Slave Input ,主设备数据输出,从设备数据输入。

③SCLK--Serial Clock ,时钟信号,由主设备产生

④CS--Chip Select,从设备使能信号,由主设备控制

SPI是串行通讯协议,数据是以一位一位的传输的,这也是SCLK时钟线存在的原因。由SCK提供时钟脉冲,SDI、SDO则基于此脉冲完成数据传输。数据输出通过SDO线,数据在时钟上升沿或者下降沿改变,在紧接着的下降沿或者上升沿读取数据,完成一位数据传输,输入也是同样的道理。

在点对点的通信中SPI不需要寻址操作,且为全双工,显得简单高效。在多个从设备的系统中,每个从设备需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。

缺点:没有指定的流控制,没有应答机制确认是否收到数据

SPI设备选择

SPI是[单主设备( single-master )]通信协议,这意味着总线中的只有一支中心设备能发起通信。当SPI主设备想读/写[从设备]时,它首先拉低[从设备]对应的SS线(SS是低电平有效),接着开始发送工作脉冲到时钟线上,在相应的脉冲时间上,[主设备]把信号发到MOSI实现“写”,同时可对MISO采样而实现“读”,如下图:

SPI数据发送接收

SPI主机和从机都有一个串行移位寄存器,主机通过向它的SPI串行寄存器写入一个字节来发起一次传输。

1. 首先拉低对应SS信号线,表示与该设备进行通信

2. 主机通过发送SCLK时钟信号,来告诉从机写数据或者读数据。这里要注意,SCLK时钟信号可能是低电平有效,也可能是高电平有效,因为SPI有四种模式。

3. 主机(Master)将要发送的数据写到发送数据缓存区(Menory),缓存区经过移位寄存器(0~7),串行移位寄存器通过MOSI信号线将字节一位一位的移出去传送给从机,,同时MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区。

4. 从机(Slave)也将自己的串行移位寄存器(0~7)中的内容通过MISO信号线返回给主机。同时通过MOSI信号线接收主机发送的数据,这样,两个移位寄存器中的内容就被交换。

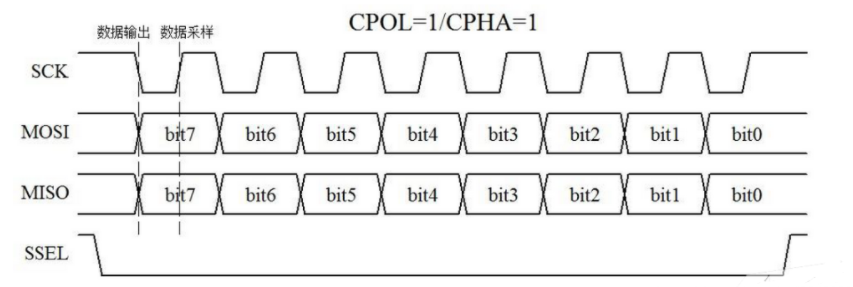

SPI通信的四种模式

时钟极性(CPOL)定义了时钟空闲状态电平:

CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时

CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时

时钟相位(CPHA)定义数据的采集时间。

CPHA=0,在时钟的第一个跳变沿(上升沿或下降沿)进行数据采样。,在第2个边沿发送数据

CPHA=1,在时钟的第二个跳变沿(上升沿或下降沿)进行数据采样。,在第1个边沿发送数据

1)Mode0:CPOL=0,CPHA=0

2)Mode1:CPOL=0,CPHA=1

3)Mode2:CPOL=1,CPHA=0

4)Mode3:CPOL=1,CPHA=1

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

通信特点

1、SPI优点

①支持全双工通信

②通信简单

③数据传输速率块

2、缺点

①没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据可靠性上有一定的缺陷。

3、特点

①高速、同步、全双工、非差分、总线式

②主从机通信模式

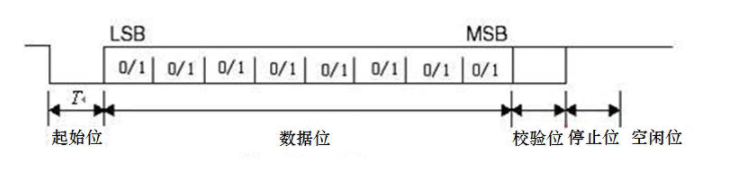

UART通信协议

UART(Universal Asynchronous Receiver/Transmitter),通用异步收发传输器。是一种通用的串行总线,用于异步通信,可以实现全双工传输和接收。工作原理是将传输数据的每个字符一位接一位地传输。

通信协议

起始位:发送逻辑“0”表示传输字符开始

数据位:可以选择5/6/7/8位,构成一个字符,通常采用ASCLL码,从低位开始传送,靠时钟定位。

奇偶校验位:数据位加上这一位,使得“1”的位数成为奇校验或者偶校验,以此来检验数据位传送的正确性。

停止位:不仅表示传输结束,而且还提供计算机校正的时钟同步的机会。

空闲位:处于逻辑“1”,没有数据传输。

波特率:是衡量数据传送速率的指标,表示每秒传送的符号数。

传输时序

通信过程

发送过程

当检测到发送命令的上升沿,启动数据发送。先发送起始位‘0’;再按照低位在前、高位在后的顺序发送数据位;然后根据数据位异或计算得到的奇(偶)校验值,作为校验位发送;最后发送停止位‘1’。具体时序如下:

外部:数据准备→发送命令置‘1’;

内部:检测发送命令上升沿→计数器启动→发送起始位、数据位、奇偶校验位、停止位→计数器清零→检测发送命令上升沿。

接收过程:

当检测到接收数据线rx的下降沿时,表示一个数据包的起始位到来,启动数据接收。先接收起始位,仅作检测作用;再接收数据位,存储在数据寄存器中,当接受完最后一位数据位时,数据读取完成标志置‘1’;再检验奇偶校验位,若不正确则数据错误标志置‘1’;再接收停止位‘1’,若不正确则帧错误标志置‘1’。具体时序如下:

内部:检测rx下降沿→计数器启动→接收起始位‘0’→接收数据位→接收完最后一位数据,数据读取完成标志置‘1’→检验奇偶校验位→接收停止位‘1’→计数器清零→检测rx下降沿;

外部:检测数据读取完成标志上升沿→读取所接收数据。

计数器:

串口通信中,时钟一般设置为波特率的多倍频(如16倍),这是因为只有在每一位的中心位置读取数据,才能确保数据的正确性,靠近位的边沿读取数据的话,容易受到器件本身电平跳变快慢的影响,具有很大的不稳定性。当时钟是16倍的波特率时,每一位的长度有16个时钟周期,我们可以选择在第8个时钟上升沿读取数据,或者取第7、8、9个时钟所读取数据相与,以保证每一位数据的准确性。

优点

仅使用两根电线

无需时钟信号

具有奇偶校验位以允许进行错误检查

只要双方都设置好数据包的结构

有据可查并得到广泛使用的方法

缺点

数据帧的大小最大为9位

不支持多个从属系统或多个主系统

每个UART的波特率必须在彼此的10%之内

————————————————

原文链接:https://blog.csdn.net/m0_37573557/article/details/121401455

原文链接:https://blog.csdn.net/as480133937/article/details/105764119/

原文链接:https://blog.csdn.net/weixin_43664511/article/details/103038303